electronica Nov 2014

32

M

ICROCONTROLLERS

complementary pairing, half-cycle reload and

up to 4 fault inputs for global fault detection.

Half-cycle reload increases control algorithm

efficiency by pre-loading values prior to next

edge of PWM, requiring fewer tasks to be

performed on a PWM transition. Managing

the FTM–ADC relationship is the program-

mable delay block that delays triggering from

the FTMs to the ADCs and helps to define

conversion sample points for precise rotor

position detection in sensorless applications.

Additional analog peripherals include dual

comparators that detect motor over-current/

voltage fault conditions triggering PWM safe

state shutdown, and a 12-bit DAC for config-

uring fault levels in software. With many low-

end designs subject to strict price pressures

(particularly consumer products), these fea-

tures help minimize BOM costs through the

elimination of external circuitry.

Kinetis KV1x MCUs offer 16 or 32 KB of flash

memory with IIC, SPI and UART communi-

cation interfaces. A cyclic redundancy check

(CRC) module can be used in conjunction

with the DMA to satisfy IEC 60730 hardware

safety requirements such as periodic calcu-

lation of the CRC checksum in flash mem-

ory. For low-power applications, multiple

low-power modes, watt-saving architectural

techniques and autonomous, power-smart

peripherals can also be leveraged. With this

level of feature integration (not to mention

the free enablement support), it is reason-

able to expect the KV1x family to be priced

beyond the reach of most entry-level design

budgets where cost dominates performance

and peripheral selection.

This is not the case as intelligent use of 90nm

technology sets the KV16 MCU in a 32LQFP

package at a starting price of $0.99 (USD,

10,000-unit quantities), with additional

48LQFP and small footprint 5mm x 5mm

32QFN packages priced accordingly. Situated

further up the Kinetis V series is the KV3x

family that addresses mid-range BLDC and

PMSM motor designs and features the ARM

Cortex-M4 core with DSP instruction support

and a floating point unit. Core frequencies

range from 100-120 MHz and flash memory

from 64-512 KB with an optional external bus

interface for off-chip system expansion. A fac-

tory-installed, flash based bootloader enables

quick and easy programming of the MCU

during development, final product manufac-

turing or in the field.

The flagship of the Kinetis V series is the

KV4x family which targets advanced PMSM

and ACIM designs that require high dynamic

control. Engineered for optimal performance,

it also incorporates the ARM Cortex-M4 core

but at an increased frequency of 150 MHz.

Code is executed from up to 256 KB of flash

memory via a 128-bit wide interface which

helps minimize CPU wait states. With up to

30 timer channels – 12 provided by the highly

flexible Enhanced FlexPWM (eFlexPWM)

module – the KV4x family has no trouble

supporting multiple three-phase motors con-

currently. Motor speed/position detection

comes from two cyclic 12-bit ADCs with sam-

ple rates of 1.9 or 4.1 Msps depending on the

device selected. These can be triggered by any

module connected to the internal peripheral

crossbar of the MCU, including timers, analog

comparators or GPIO.

The KV4x family’s high degree of feature inte-

gration enables up to 30 PWM outputs, 38

ADC channel inputs, as well as CAN, UART

and SPI interfaces to be housed in a 100-pin

LQFP package. All Kinetis V series MCUs

operate from 1.71 to 3.6V and from -40C to

105C. Production-qualified Kinetis KV1x and

KV3x MCUs are available now; KV4x MCUs

are currently sampling and are planned to

enter production early in Q1 2015.

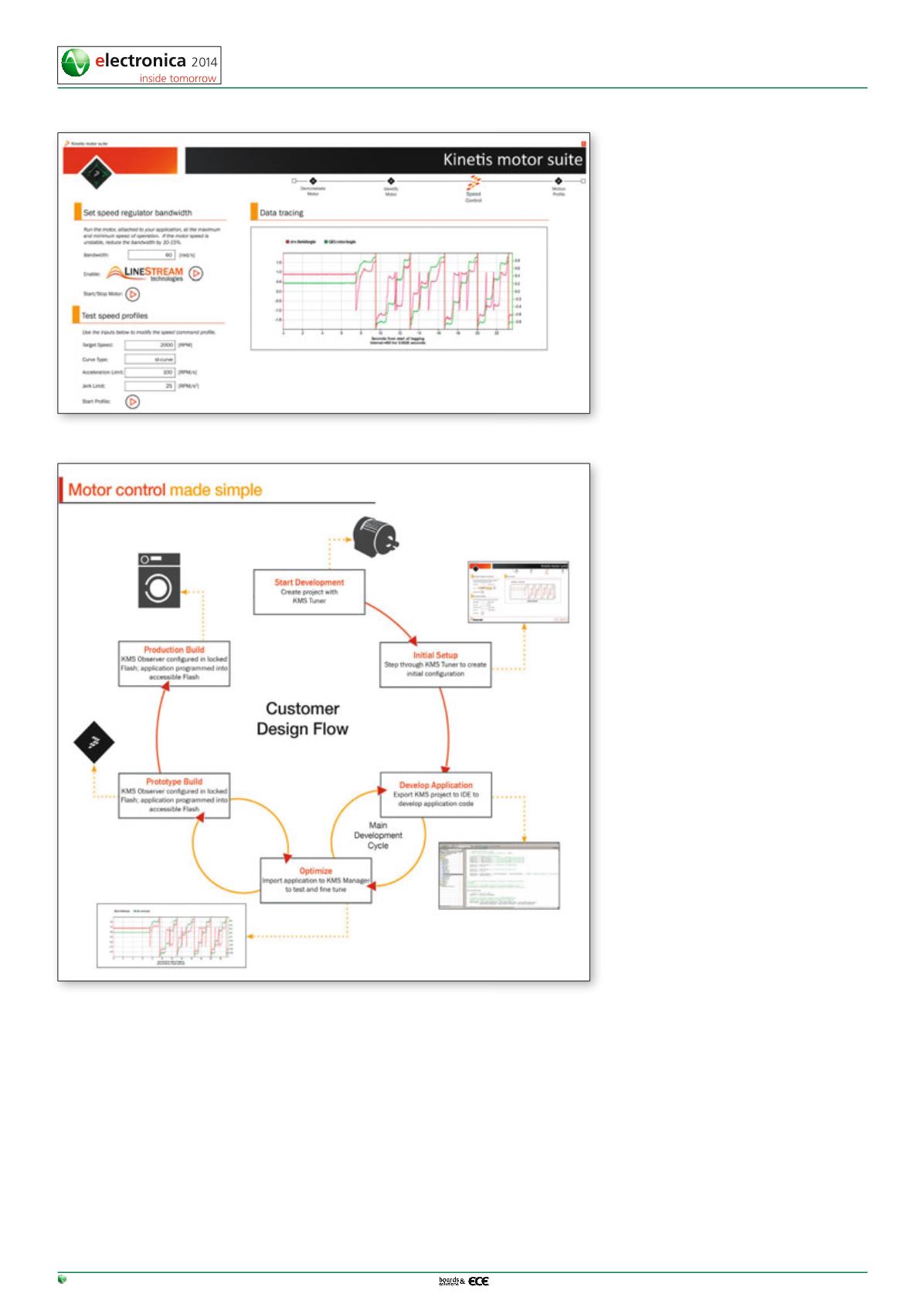

Kinetis Motor Tuner GUI

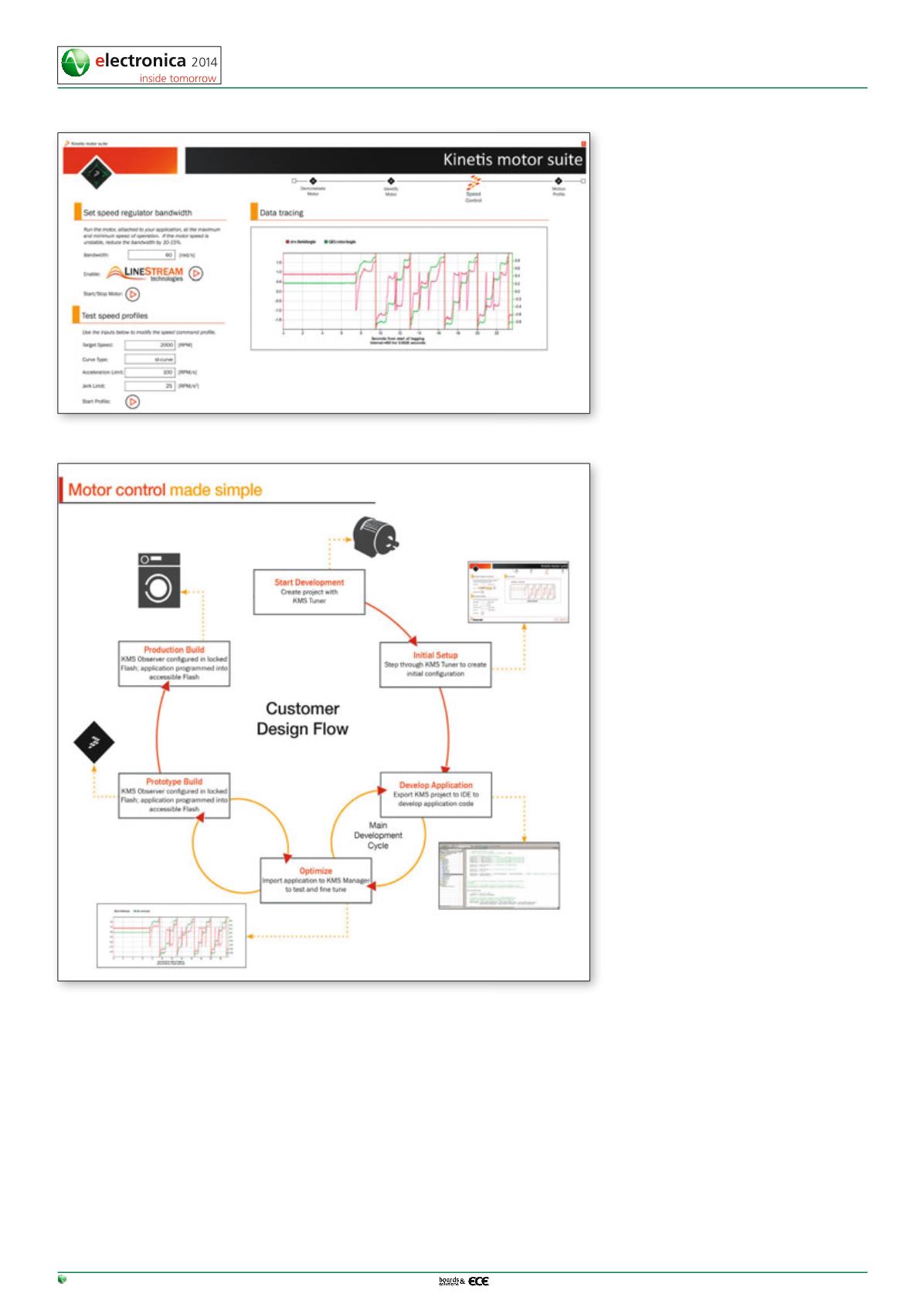

Kinetis Motor Suite design flow